# PARALLEL PROCESSING SYSTEM (PPS) DATA SHEET

# GENERAL PURPOSE KEYBOARD AND DISPLAY CONTROL (GPKD)

# INTRODUCTION

This document describes General Purpose Keyboard and Display circuit P/N 10788, manufactured by the Microelectronic Device Division of Rockwell International. This versatile circuit provides the optimum method of interfacing the Rockwell Parallel Processing System (PPS) Microcomputers to a wide variety of keyboards and display devices. The General Purpose Keyboard and Display (GPKD) circuit interfaces the functional circuits in the PPS with the majority of business machine, Point-of-Sale (POS), and calculator keyboards and displays.

The General Purpose Keyboard and Display circuit (GPKD) connects directly with the PPS data bus. The GPKD is initialized by the Synchronized Power-On (SPO) signal from the CPU.

The keyboard controller functions of the GPKD strobe up to 64 single-pole, single-throw momentary switches on an  $8 \times 8$  matrix and provide a 7.68 msec debounce delay for these switches. A 9-level, 8-bit key buffer allows up to nine key inputs to be stored until the PPS processes them. Inputs can be entered at an operating speed of 7.68 msec/character.

The display controller functions of the GPKD synchronize and strobe up to 16 characters of display data which are outputted in two hexadecimal groups. The two hexadecimal groups of data, designated as Group A and Group B, may be used as one group of 8-bit data or several groups of data composed of less than 8 bits. A typical application of the data display is to use 4 bits of data for numeric display, 2 bits for decimal point and comma, and the remaining 2 bits for display up to 32 status indicators. It is also possible to display 32 consecutive digits of numeric data and some symbols when two 16-digit hexadecimal groups are treated as one 32-digit hexadecimal code.

# **FEATURES**

#### **KEYBO**ARD

- Nine-Key Buffering

- Two-Key Rollover

- 7.68 msec Key Debounce Delay

- Handle up to 64 keys on 8 x 8 matrix

- Chip Address Strap Encoded

- Initialized at Power On (SPO)

#### DISPLAY

- Display up to 16 characters

- 32 Digits of Display Possible

- Two 16-Digit Display Buffers

- Two Sets of Hexadecimal Code Outputs for Display

- TTL Compatible Interface

- 5% Duty Cycle

SC6 1 20 T/D5 42 1/D6 41 SC5 SC7  $\overline{}$ SPO 3 40 1/D7 4 39 1/D1 W/10 c 38 1/D4 1/D8 6 1/D2 37 DAI 7 36 c 1/D3 8 DA2 35 DBS ٩ DA3 34 ¥ 7 c X6 DA4 10 33 32 κ5 vss DB1 X4 12 31 D82 13 30 xз DB3 14 29 X2 DB4 28 15 27 ดเหล็ 16 xn 26 VDD c 17 25 CLKA YO 6 18 24 19 23 Y1 Y2 20 21 22

**GPKD** Pin Configuration

C Rockwell International Corporation 1975 All Rights Reserved Printed in U.S.A Specifications subject to change without notice Revision 1, March 1976

# FUNCTIONAL DESCRIPTION

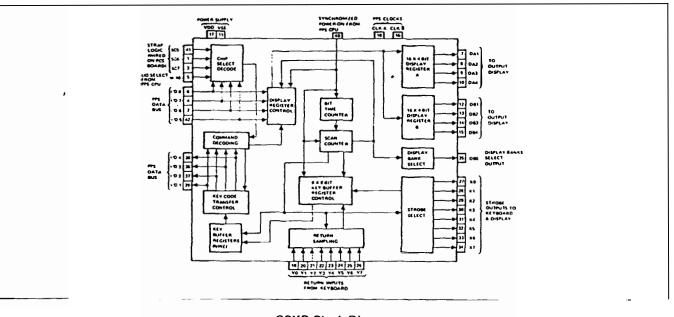

The GPKD block diagram shows the various functional circuits in the GPKD. The following paragraphs discuss the functional elements of the GPKD listed below:

Chip Select Decode Command Decoding Bit Time Counter Scan Counter Display Register Control Display Register A Display Register B Display Bank Select Strobe Select Return Sampling Key Buffer Register Control Key Buffer Registers Key Code Transfer Control

## CHIP SELECT DECODE

The chip select decode circuit compares the chip address data on data bus lines 1/D5, 1/D6, and 1/D7 to the data on chip select straps SC5, SC6, and SC7. If the result is the same and the W/IO and 1/D8 lines are true, the GPKD is selected.

#### COMMAND DECODING

The command decoding circuit determines which of the eight GPKD commands will be executed. The chip select decode logic enables the command decoding, which decodes the command inputs I/D1, I/D2, I/D3 and I/D4.

#### **BIT TIME COUNTER**

The bit time counter divides the PPS clock frequency by 8 to provide increment timing of the scan counter. One bit time equals one basic PPS cycle time, (typically 5  $\mu$ sec).

## SCAN COUNTER

The scan counter provides timing signals for the display register control, display bank select, return sampling, key buffer register control, and strobe select functions. The scan counter updates its count once every 8 bit times by using the bit time counter output.

The 8-bit codes generated by the scan counter represent corresponding keys on the key matrix. Upon a detection of a key depression, the scan counter content at that moment represents the depressed key and is transferred to the first key buffer register.

## DISPLAY REGISTER CONTROL

The display register control logic controls load, shift hold, turn on, and turn off of display registers A and B. The scan counter provides the synchronizing signal to the display register control, and the command decoding function provides the signal that controls the modes of the display registers.

#### **DISPLAY REGISTERS A AND B**

Display registers A and B are used to store display data. Each display register consists of 16 4-bit storage registers. The contents of the storage registers can be changed only by I/O commands and, therefore, are independent of the system operations controlled by other than I/O commands. The display registers take the data from the data bus ID/5, ID/6, ID/7 and ID/8. Loading time and outputting of the display registers are controlled by display register control logic, which is governed by microprogrammed commands and the scan counter.

Each of the two display registers has four parallel open drain outputs each of which is capable of driving one TTL load. These outputs are synchronized with the strobe select lines and display bank select line. The outputs of display register A are designated DA1, DA2, DA3 and DA4, and the outputs of display register B are designated UB1, DB2, DB3 and DB4.

#### DISPLAY BANK SELECT

The display bank select combined with the eight strobe lines provides scanning for up to 16 characters of display. The display bank select output is designated as DBS. A VSS level on the DBS line selects the lower eight strobes and the VDD level on DBS selects the upper eight strobes, thus yielding a total of 16 strobes.

#### STROBE SELECT

The strobe select circuit sequentially outputs eight strobe signals designated X0 through X7, each on a separate output line. The first strobe occurs on X0, the second strobe occurs on X1, and strobes continue in sequence through X7, after which the strobes restart at X0. The strobes are used in forming an 8 by 8 XY keyboard matrix in which X corresponds to the strobe select lines and Y to the keyboard return lines. The strobe select, in conjunction with the display bank select, is also used for multiplexing up to 16 characters of display.

#### **RETURN SAMPLING**

The return sampling circuit tests the states of key matrix return lines from the keyboard. The results of the tests are used in the key buffer register control logic to determine the key status. The eight return lines from the keyboard XY matrix are designated Y0 through Y7.

## **KEY BUFFER REGISTER CONTROL**

The key buffer register control performs the following two functions: (1) loads the key code generated by the scan counter into the first buffer register when the return sampling logic detects a key closure, and (2) controls the "first in, first out" operation of the key buffer registers.

## **KEY BUFFER REGISTERS**

The GPKD has nine 8-bit key buffer registers to store key codes (keyboard entries) until transferred out by PPS request. Upon a key closure detection, the corresponding code generated by the scan counter is loaded into the first key buffer register, then transferred to the next key buffer register if it is empty. If all nine buffer registers are full and another key is depressed the MSB of the ninth key code goes from 0 to 1. A "1" in the MSB indicates to the CPU that the key buffer register storage capacity has been exceeded, and that one or more key entries may have been lost. The CPU will reset this error condition using the KER instruction. The data in the first eight buffer registers will be accepted by the CPU as valid data.

#### KEY CODE TRANSFER CONTROL

The key code transfer control outputs data from the last key buffer register to the I/D bus upon request by the PPS CPU. The output of data is handled on a "first in, first out" basis.

## INTERFACE

The interface considerations of the GPKD are divided into three functions for explanation purposes. These functions are as follows:

PPS CPU Interface to GPKD Keyboard Interface to GPKD Display Interface to GPKD

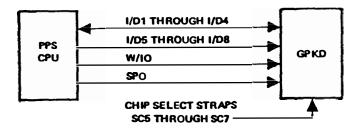

## PPS CPU INTERFACE TO THE GPKD

Physical interconnection of the CPU to the GPKD is accomplished by connecting CPU lines to GPKD circuit pins of the same designation. The interface is shown in the figure below. CPU lines connected to the GPKD are 1/D1 - 1/D8, SPO, and W/10.

## KEYBOARD INTERFACE TO GPKD

The GPKD has 16 lines which form a keyboard matrix. Eight of the lines are strobe lines designated X0 through X7 and the other eight lines are return lines designated Y0 through Y7. Two IOL instructions are required to read in a designated key location, one instruction for strobe line data and the other instruction for return line data.

## DISPLAY INERFACE TO GPKD

Two groups of four 16-bit registers are used to store display data. Each of these two register groups has four outputs and each output is capable of driving one TTL load. The GPKD is designed to use TTL logic to interface to the many different commercial displays.

# **GPKD Block Diagram**

#### UPERALING GRANAGI LINGING

#### Supply Voltage:

VDD = -17 Volts ±5%

(Logic "1" = most negative voltage V<sub>1L</sub> and V<sub>OL</sub>.) VSS = 0 Volts (Gnd.)

(Logic "0" = most positive voltage  $V_{1H}$  and  $V_{OH}$ .)

## System Operating Frequencies:

199 kHz or 256 kHz.

Device Power Consumption:

200 m w

Input Capacitance:

<5 pf

#### Operating Temperature (TA):

$0^{\circ}$ C to 70°C. (TA = 25°C unless otherwise specified.)

١,

Storage Temperature: .55°C to 120°C.

## **ABSOLUTE MAXIMUM RATINGS**

## Supply Voltage

VDD-VSS = 27 volts maximum. Input Voltage with respect to VSS -27 volts maximum.

Maximum positive voltage on any pin +0.3 volts.

|                                                                |                            |                                    | LIMITS (VSS = 0V)        |          |                | LIMITS (VSS = +5V)       |                 |                | l 1        | TEST                                                                            |

|----------------------------------------------------------------|----------------------------|------------------------------------|--------------------------|----------|----------------|--------------------------|-----------------|----------------|------------|---------------------------------------------------------------------------------|

| FUNCTION<br>Supply Current (Average)                           |                            | SYMBOL                             | MIN                      | ТҮР<br>4 | MAX<br>11      | MIN                      | <b>TYP</b><br>4 | MAX<br>11      | UNIT<br>mA | CONDITIONS<br>VDD = -17.85V<br>VSS = 0V<br>F = 256 kHz<br>T <sub>A</sub> = 25°C |

|                                                                |                            | ססי                                |                          |          |                |                          |                 |                |            |                                                                                 |

| Input and Output Characteristics - System Bus                  |                            |                                    |                          |          |                |                          |                 |                |            | VDD = -17V ±5%                                                                  |

| I/D <sub>1-4</sub>                                             | 1′D <sub>5-8</sub><br>₩/10 |                                    | -1.5<br>-6.5             |          | +0.3<br>-17.85 | +3.5<br>•1.5             |                 | +5.3<br>•12.85 | ><br>>     | VSS = 0V                                                                        |

|                                                                |                            | V <sub>OH</sub><br>Vol             | -1.0<br>-7.5             |          | +0.3<br>-17.85 | +4.0<br>-2.5             |                 | +5,3<br>-12.85 | v<br>v     |                                                                                 |

| SC5.7                                                          |                            | V <sub>IH</sub><br>V <sub>IL</sub> | -1.5<br>-13.0            |          | +5.3<br>-17.85 | +3.5<br>-8.0             |                 | +5.3<br>-12.85 | ><br>>     |                                                                                 |

| SPO                                                            |                            | V <sub>IH</sub><br>VIL             | ·1.0<br>·7.5             |          | +0.3<br>-17.85 | +4.0<br>∙2.5             |                 | +5.3<br>•12.85 | ><br>>     | OR                                                                              |

| CLKA<br>CLKB                                                   |                            | V <sub>IH</sub><br>VIL             | -0.5<br>-10.0            |          | +0.3<br>-17.85 | +4.5<br>-5.0             |                 | +5.3<br>-12.85 | v<br>v     |                                                                                 |

| Input and O                                                    | utp_: Characteristics      | - External Interf                  | ace                      |          |                |                          |                 |                |            |                                                                                 |

| Y0.7                                                           |                            | ViH<br>ViL                         | -4.0<br>- 13.0           |          | +0.3<br>-17.85 | +1.0<br>-8.0             |                 | +5.3<br>·12.85 |            |                                                                                 |

| X <sub>0.7</sub> . DA <sub>1.4</sub> , D≞ <sub>1.4</sub> , DBS |                            | V <sub>OH</sub><br>V <sub>OL</sub> | NOTE 1<br>floating (≥5M) |          |                | NOTE 1<br>floating (≥5M) |                 |                | Ω          | <pre>`VDD = 12V + 59<br/>VSS = +5V ±5%</pre>                                    |

**REGIONAL SALES OFFICES**

.

EASTERN REGIONAL MANAGER JIM PIERCE RL 2 Box 525 Riverhead N. Y. 11901 Phone: 515 979-0183

S. EASTERN REGIONAL MANAGER RON JANSSEN 3500 McC: Piace Atlanta, Cr. 20340 Phone: 4(4: 458.2263 JAPAN SALES MANAGER SHIGE MURASE Rockwell Interational Overseas Corp. Ichibanicho Central Bldg. 22-1 Ichibanicho Chivoda ku Tokyo 102, Japan Phone: 265-8803

CENTRAL REGIONAL MANAGER J/M SMITH 2855 Coolidge Frad Suite 101 Troy, Mich, 48024 Phone: 313/435-1638

Rockwell International Microelectronic Device Division

MIDWEST REGIONAL MANAGER ALLAN CAREY 2520 E Higgins Road Suite 200 13 Eve Grave Village, I., 60007 Phone - 212/439-1713 EUROPEAN SALES MANAGER ANDRE KOBEL Rickwell International Gene-Microelectronic Device Division Frauenholerstrasse 11 D 8033 Munchen Marticistens Germany Phone: 8599575

WESTERN REGIONAL MANAGER BILL TRELEAVEN BOR 3669 Anaherm, Ca. 92803 Phone: 214/622,3699

For assistance, call or write the office nearest you.